Formal Verification Tool Reviews & Metrics

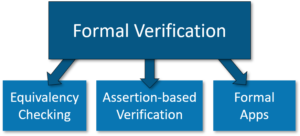

Formal verification tools include an array of technologies that use static analysis used to prove or disprove the correctness of hardware or software behavior with respect to a certain formal specification or property.

Formal verification contrasts with dynamic verification techniques such as simulation. In general, the two methods are considered complementary elements in a verification methodology, although there is often discussion as to which method is best suited for a given situation.

In addition to multiple commercial formal verification tools in the industry, there are formal apps which offer automation of certain tasks, to enable designers to do some early checking.

Formal Verification Product Reviews

Below are user reviews for formal verification tools and formal apps over the past few years.

- The dates are based on the year the reviews were published.

- In some years, there were so many formal verification tool reviews that there are 3 sections.

The products discussed include Cadence JasperGold, OneSpin DV-Verify, Mentor Questa FV & Synopsys VC Formal.

Additionally, there is an article that compiles design and verification engineers’ insights comparing Formal Verification vs. RTL Simulation.

Formal Verification Tools – Metrics

The primary metrics that the system and semiconductor verification engineers referenced when reviewing the products are listed below.

Formal Verification Metrics covered:

- Best applications for formal

- Learning curve & Ease of use

- Number & Power of underlying engines

- Performance & Capacity

- Equivalency checking

- Debug Visualization & Usability

- Contrast with Simulation approach

Formal Apps Covered:

- Sign-off

- Sequential Equivalence Check

- Coverage Unreachability

- Formal Property Verification

- Reverse Connectivity

- Register

- Connectivity

- Safety Analysis